ALINX Brand Intel ALTERA FPGA Development Board Cyclone 10 10CL006 10CL016 10CL025 Gigabit Ethernet HDMI CMOS Camera Interface (AX1016, FPGA Board + Platform Cable USB + ADDA Acquisition Module) : Electronics

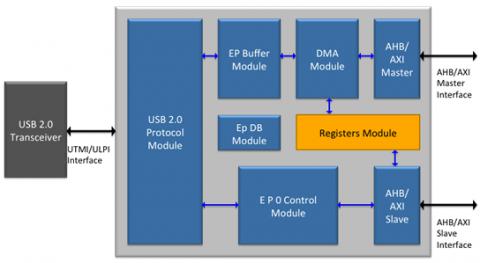

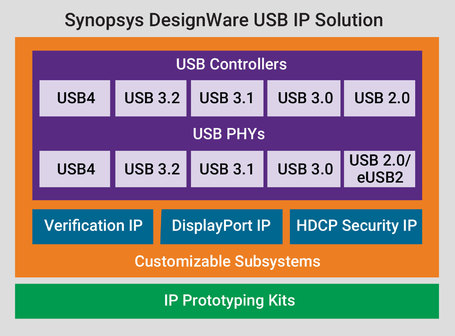

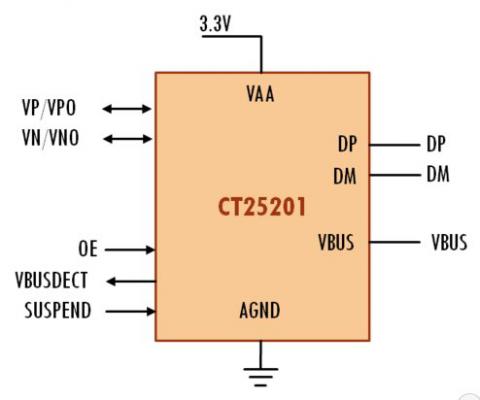

GOWIN Releases USB 2.0 PHY and Device Controller IP for Their FPGA Products | Civil + Structural Engineer magazine

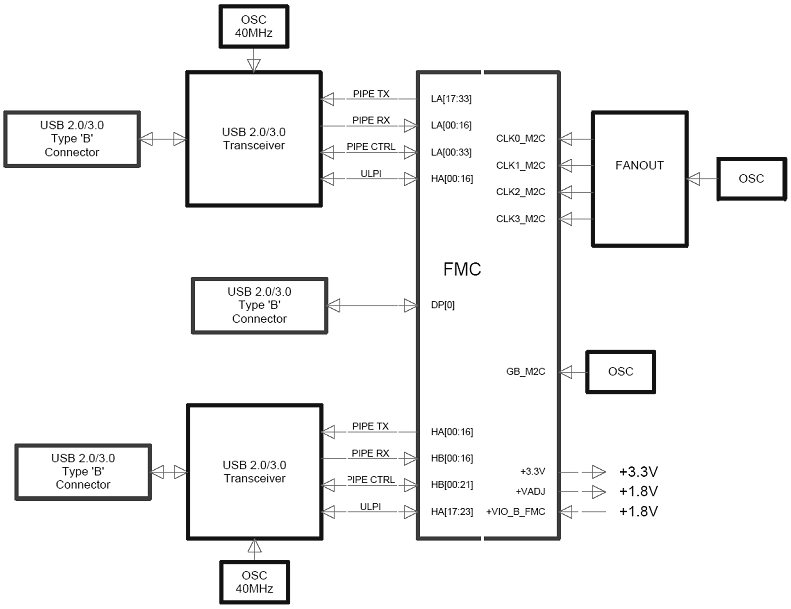

![DesignGateway Co., Ltd. The Expert of IP Core [USB3.0-IP] DesignGateway Co., Ltd. The Expert of IP Core [USB3.0-IP]](https://dgway.com/products/IP/ABseries/image/AB08-USB3HSMC.JPG)